# SIMADYN D Digital Control System

**User Manual**

# Processor module PG26

Edition 05.95 DK-Nr. 222342

## User Manual, Processor module PG26

| Edition |                       | Edition status |

|---------|-----------------------|----------------|

| 1       | Processor module PG26 | 06.93          |

| 2       | Processor module PG26 | 05.95          |

|         |                       |                |

|         |                       |                |

Copying of this document and giving it to others and the use or communication of the contents thereof is forbidden without express authority. Offenders are liable to the payment of damages. All rights are reserved in the event of the grant of a patent or the registration of a utility model or design.

We have checked the contents of this Manual to ensure that they coincide with the described hardware and software. However, deviations cannot be completely ruled-out, so we cannot guarantee complete conformance. However, the information in this document is regularly checked and the necessary corrections included in subsequent editions. We are thankful for any recommendations or suggestions.

# **Contents**

| Warning information                                     | 1   |

|---------------------------------------------------------|-----|

| 1. Order number, Validity Definition                    | 3   |

| 2. Functional Description                               |     |

| 3. Board Design                                         | 6   |

| 4. Application Notes                                    | 6   |

| 5. Technical Specification                              | 9   |

| 6. Pin Allocation of the PG26                           | 11  |

| 6.1.Pin Allocation of the Serial Interface X01          | .11 |

| 6.2. Pin Allocation of the External Signals X5          | 11  |

| 6.3. Pin Allocation of the Binary inputs and outputs X6 | 12  |

| 6.4. Pin Allocation of the SITOR Interface X7M, X7S     |     |

| 6.5. Allocation of the Measurement Jacks X10 - X15      |     |

| 6.6. Power converter specific signals X200              |     |

| 6.7. Switch set-ups S1-S4                               |     |

| 7. Mask of the PG26 in the Master Program               |     |

| 8. Appendices                                           |     |

| 8.1. Block diagram                                      | 16  |

| 8.2. Scale drawing and table of the plug connector      |     |

| 8.3. Allocation plan                                    |     |

| 8.4. Scale drawing of the cable for special lengths     | 16  |

| 9. Miscellaneous                                        | 16  |

| 10. ECB instructions                                    | 18  |

| arning information |  |  |  |

|--------------------|--|--|--|

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

1

#### NOTE!

The information in this Manual does not purport to cover all details or variations in equipment, nor to provide for every possible contingency to be met in connection with installation, operation or maintenance.

Should further information be desired or should particular problems arise which are not covered sufficiently for the purchaser's purposes, please contact your local Siemens office.

Further, the contents of this Manual shall not become a part of or modify any prior or existing agreement, committment or relationship. The sales contract contains the entire obligation of Siemens. The warranty contained in the contract between the parties is the sole warranty of Siemens. Any statements contained herein do not create new warranties nor modify the existing warranty.

## Warning information

#### WARNING!

Electrical equipment has components which are at dangerous voltage levels.

If these instructions are not strictly adhered to, severe bodily injury and material damage can result.

Only appropriately qualified personnel may work on this equipment or in its vicinity.

This personnel must be completely knowledgeable about all the warnings and service measures according to this User Manual.

The successful and safe operation of this equipment is dependent on proper handling, installation, operation and maintenance.

#### **Definitions**

#### \* QUALIFIED PERSONNEL

For the purpose of this User Manual and product labels, a "Qualified person" is someone who is familiar with the installation, mounting, start-up and operation of the equipment and the hazards involved. He or she must have the following qualifications:

- 1. Trained and authorized to energize, de-energize, clear, ground and tag circuits and equipment inaccordance with established safety procedures.

- 2. Trained in the proper care and use of protective equipment in accordance with established safety procedures.

- 3. Trained in rendering first aid.

#### \* DANGER

For the purpose of this User Manual and product labels, "Danger" indicates death, severe personal injury and/or substantial property damage will result if proper precautions are not taken.

#### \* WARNING

For the purpose of this User Manual and product labels, "Warning" indicates death, severe personal injury or property damage can result if proper precautions are not taken.

## \* CAUTION

For the purpose of this User Manual and product labels, "Caution" indicates that minor personal injury or material damage can result if proper precautions are not taken.

#### \* NOTE

For the purpose of this User Manual, "Note" indicates information about the product or the respective part of the User Manual which is essential to highlight.

#### CAUTION!

This board contains components which can be destroyed by electrostatic discharge. Prior to touching any electronics board, your body must be electrically discharged. This can be simply done by touching a conductive, grounded object immediately beforehand (e.g. bare metal cabinet components, socket protective conductor contact).

#### WARNING!

Hazardous voltages are present in this electrical equipment during operation.

Non-observance of the safety instructions can result in severe personal injury or property damage.

It is especially important that the warning information in all of the relevant Operating Instructions are strictly observed.

# 1. Order number, Validity Definition

6DD 1601 - 0AF0 PG26 Processor board DC 16 Mhz

for 12 pulse cascade connections. Software version from 3.2

# 2. Functional Description

The processor module PG26 is utilized in the SIMADYN D system for the triggering of 12 pulse line commutated power converters, installed as a cascade of two 6 pulse bridges on 30 degree phase shifted power lines.

The hardware is based on the PG16 board /1/, whereby the trigger signals for the second converter are generated on a sub-module and can be accessed at a second SITOR interface.

The high processing power of the 16MHz processor board permits the calculation of the torque shell and therefore the trigger pulse output every 30 degrees. The function module TG12 generates a signal for the correct pulse assignment of the 30 degree lagging power converter system (slave).

The board can be programmed for both the user software and the system firmware (operating system, monitor program as well as the function module code) on plug-in memory sub-modules (MSx) located in the X50 connector. The user code runs on the processor under the SIMADYN D real time operating system. This guarantees interrupt controlled cycle times of ≥ 1ms, dependent upon the configuration.

Four binary inputs and four binary outputs are available for fast data exchange with other processor modules or for messages from/to the installation (plug connector X6). The binary inputs can also be declared as interrupt inputs via the software. All four binary inputs can be declared as interrupt inputs by the software. The processor interrupts cyclic processing at the occurrence of an interrupt at one of these inputs and starts the interrupt function packet "Process Interrupt Job" (PIJ) processing.

The serial interface (connector X01) is designed purely as a service interface. No communication can be configured via this interface. A dialog is only possible with the Hex monitor and only with the corresponding hybrid board installed.

The seven segment display H1 on the board front plate shows the configured processor number in normal operation. The display flashes an error code, see /2/, when a fault occurs on the board.

The Hex monitor can be activated, when an error message is being displayed, by pressing the S1 key.

The double test jack X10 and X11 can be used to force a board reset (new start). This is implemented by jumpering the jacks with a switch or a shorting plug. The test jack X10 is also the ground connection for the test signals at X12-X15.

A 50 pin test connector X4 is available on the board for hardware diagnostics using a logic analyzer or a recorder. The recorder also requires a 10 pin connector X9.

Three "watchdogs" are available for each processor board for monitoring the functionality of the hardware and software.

The hardware monitor checks:

- ready signal timeouts during system bus accessing

- double address decoding errors

- whether addresses are accessed, that are not used

- system bus fault messages

The software monitor checks:

- whether the processor is still running a cyclic program

- whether the interrupt controller of the serial interfaces, timer and inputs are operating correctly.

A "Non Maskable Interrupt" (NMI) is generated when the watchdog detects a fault. The processor attempts to eliminate the fault and return to cyclic operation. If the fault is being caused by the processor, then it switches to an inactive state, activates the red dot on the seven segment display and the "system fault" line on the bus.

The processor board PG26 has a standard interface for controlling the SITOR thyristor sets. The corresponding signals are implemented on a 50 pin connector socket (X7M, X7S). The connector on the mother board X7M always acts as the master.

The following signals are required from the master converter for the processor board:

- \* synchronization voltage

- \* monitoring signals

- \* two signals for the detection of the rotating field direction

- \* current zero transgression

- \* current actual value as proportional frequency value

- \* voltage actual value as proportional frequency value

The slave power converter must supply the following signals:

- \* synchronization voltage

- \* monitoring signals

- \* two signals for the detection of the rotating field direction

The master interface X7M signals are evaluated by the software and generate, when faults are detected, the messages described in /3/. Software checks of the slave interface X7S are not possible. The supplementary hardware for the second SITOR interface detects the following faults and displays them using the H20-23 LED's. The checks can be disabled with the switches S1 and S2.

\* H20, green : lit when no faults have been detected

\* H21, red : lit as long as a SITOR monitoring fault at

X7M or X7S is detected

\* H22, red : lit when no right hand rotating field is detected at X7S,

the monitor utilizes the signals L12, L13 from

X7S, it is disabled when S1 is closed.

\* H23, red : lit for incorrect master/slave assignment at X7M, X7S.

Evaluation of both synchronization voltages,

disabled when S2 is closed.

The processor board PG26 supplies the trigger pulses for the thyristors of the SITOR set for the torque direction I and torque direction II.

The diode pair H10 and H11 display which torque direction is currently active.

- \* LED H10 indicates the torque direction I.

- \* LED H11 indicates the torque direction II.

Two further double test jacks (X12-X15) are available on the PG26 for the output of converter specific measurement values. The reference or ground point is jack X10 :

- \* X12: phase to phase voltage L1-L3

- \* X13: analog current actual value for the connection of a conventional meter type instrument (not available when connected via SE20)

- \* X14: Summated pulses Slave

- \* X15: Summated pulses Master (also at X5 Pin 9)

The summated pulse signals indicate the time sequencing of the trigger pulses, dependent upon the torque direction. In addition, the pulse chain sequencing of the primary and secondary pulses for thyristor 1 and the trigger pulses are modulated together, see diagram 1.

The X5 connector is designed for the supply of external signals and reading measurement signals during commissioning:

- \* external synchronization voltage

- \* external pulse disable

- \* synchronization of the pulse chain in conjunction with other PG's

- \* analog current actual value as from X12

- \* summated pulses as from X15

- \* synchronization voltage, digital after internal smoothing

- \* excitation current setpoint

## 3. Board Design

- \* connection for the local bus

- \* design for self ventilation

- \* CPU 80C186 16 MHz

- \* RAM 64 K Byte Battery backup from the power supply

- \* connector slot for the program memory module MS31,MS4,MS41,MS45

- \* 1 serial interface optional V 24, 20 mA (TTY)

- \* 4 binary inputs, non voltage isolated, interrupt controller, 24 V

- \* 4 binary outputs, non voltage isolated, 24 V, 50mA

- real time clock resolution 10 MS;Battery backup from the power supply

- \* 7 segment display for the configured processor number or error code

- \* board ID

- \* hardware and software monitoring by watchdogs

- \* test connectors for logic analyzers or recorders

- \* 50 pin SITOR interface with analog output for the excitation current control, 12 bit, 10V, 20mA

- \* SITOR interface Slave, 50 pin

- \* 50 pin diagnostic connector on the sub-module for converter specific signals

# 4. Application Notes

The processor board PG26 can be installed in both the wide rack (SR1, SR5) and the narrow rack (SR2, SR4). It requires two rack slots.

!! The board must never be inserted nor pulled when under power !!

An interface thick film circuit (hybrid module) must be installed to implement the Hex monitor dialog via the serial interface X01 .

- \* SS1: 20 mA (TTY) for PG 685

- \* SS2: V.24 (RS 232) for Televideo, PC

The hybrid module must be installed on the X51 location for the X01 serial interface.

#### WARNING: ENSURE CORRECT INSTALLATION!

Commissioning recommendations are to connect the X5 connector with an interface module SE8. All the necessary measuring signals are available at this module. Further information for commissioning see /3/.

The binary inputs and outputs are connected to the interface module SE4.1 or SE8 (SE4.1 with an additional LED status display) from the X6 connector via a 10 pin ribbon cable. The external connections to the installation are also located there (see diagram 2a).

The SITOR sets or SITOR cubicle systems with interface boards SE20.2 are connected for 12 pulse operation according to diagram 2b:

- The trigger set TG12 always synchronizes itself to the master interface X7M, current and voltage values are only evaluated here.

- the connector X7S must be connected to the power converter which is lagging by 30 degrees.

- the phase shift between both line systems must be configured at the connector DMS of the TG12 function module. The default value is 30 degrees. Compensation of any symmetry losses due to a possible cascaded transformer. Adjustment permitted between 27 and 33 degrees.

- the current control requires the total output voltage from the cascade circuit as a voltage proportional signal at X7M. The voltage acquisition of the master set, when utilizing SITOR sets, must be rewired to the total output voltage (additional plug connector between the master and the slave, see the operating manual SITOR). The maximum insulation voltage of the SITOR set must, however not be exceeded.

If several SITOR sets are operated in parallel at X7M and X7S, then the connection is implemented via the adapter board C. Details are available in the operating manual. The maximum output current of the pulse driver must not be exceeded.

Six pulse operation permits the possibility that both available interfaces X7M and X7S are directly utilized to trigger two SITOR sets connected in parallel. This only requires configuring as a six pulse trigger set and closing the switches S2 and S3 on the sub-module.

The pins 3 (15V) and 4 on the X5 plug connector must be jumpered with a shorting bridge or switch in order to enable the thyristor firing pulses. This may be implemented either directly on the X5 plug or through a binary output (24V) of a connected interface module. A daisy chain bridge can be used to jumper the pins 3 and 4 on X5. Supplying 24V always requires an additional terminal block.

The synchronization voltage supply may be selected either from an external source via the X5 connector or an internal source from the SITOR set (X7M). The default setting is the supply via X7M. The selection between X7m and X5 is implemented via software at the connector SYX in the function module TGxxx.

Each SITOR interface has 12 pulse outputs. The supply voltage is 24 V + 25%, -20%. The output current for chain pulses is 300 mA for a pulse interval of a maximum of 30 degrees.

Long duration pulses can also be generated instead of the chain pulses. The selection is implemented via software at the connector LDP in the function module TGxxx. The maximum output current of the pulse driver is halved when the modulation is disabled.

Remove the resistor R605 when an application requires the secondary pulses to be completely disabled.

#### Supplementary PG26 components:

#### a) Service Interface

\* Interface hybrid circuit SS1 (20 mA) 6DD 1688-1AA0

\* Interface hybrid circuit SS2 ( V24 ) 6DD 1688-1AB0

\* Cable PM - PG685 SC32 20 mA/10 m 6DD 1688-1DC0

#### b) Binary inputs and outputs

Cable:

\* 10 pin 2.0 m SC7 6DD 1684-0AH0

Terminal block:

\* SE4.1 6DD 1681-0AE1

8 binary inputs or outputs, non-isolated, LED display

\* SE 8 6DD 1681-0AJ0

8 binary inputs or outputs,

non-isolated

#### c) SITOR interface

#### Ribbon cable:

\* 50 pin no longer supplied by the SWE because of the high

female/male sensitivity to interference.

Can be utilized over short distances inside a cubicle without interference

sources. Customer manufacture aus SM4, SM4.1 and ribbon cable according to

SN54234, see 4656849000.11MB.

Utilization is solely the customers responsibility.

### Round cable, screened:

\* 50 pin 2 m SC17.2 6DD 1684-0BH2

female/male

\* 50 pin 10 m SC31.2 6DD 1684-0DB2

female/male

These cables consist of screened round cable with twisted pair conductors. The screening is improved by using a plug casing at the connectors.

The SWE works only supplies these prepared cables. Special lengths must be manufactured by the customer. The cables are made according to the scale drawing 4656849000.11, which also contains all the necessary order numbers. The scale drawing is contained in the appendix.

The maximum permissible distance between the PG26 and the SITOR unit is 50m with this cable!

#### Interface boards:

\* SE20.2 6DD 1681-0CA2

\* Adapter board C 6QX 5340

# 5. Technical Specification

General Data

INSULATION GROUP A to VDE 0110 (power side) paragraph 13, group 2

at 24 VDC, 15VDC, 5 VDC

AMBIENT TEMPERATURE 0 to 55 degC

STORAGE TEMPERATURE -40 to +70 degC

HUMIDITY CLASS F to DIN 40040

ALTITUDE RATING S to DIN 40040

MECHANICAL STRESS Installation in fixed vibration resistant devices

PACKAGING SYSTEM ES 902 C DIMENSIONS 233.4 x 220 mm

BOARD WIDTH 2 2/3 SPS = 2 Slot = 40.28 mm

WEIGHT 0.8 kg

CURRENT CONSUMPTION 5 VDC 2.8 A with MS4

+15 VDC 110mA -15 VDC 60mA

Vbatt 10 uA in backup operation

**BINARY INPUTS**

NUMBER 4 not voltage isolated INPUT VOLTAGE +24 V Rated value

INPUT VOLTAGE

FOR 0 SIGNAL -1 V to +6 V; or Binary inputs open

FOR 1 SIGNAL +13 V to +33 V

INPUT CURRENT

AT 1 SIGNAL Typ. 3 mA

DELAY TIME 200 us (Input filter)

**BINARY OUTPUTS**

NUMBER 4 not voltage isolated

SUPPLY VOLTAGE

-RATED VALUE 24 VDC--HARMONICS 3.6 VDC

-PERM. RANGE + 20 to + 30 V incl. harmonics -TRANSIENTS + 35 V smaller than 0,5 sec.

OUTPUT CURRENT AT 1 SIGNAL

-RATED VALUE 50 mA SHORT CIRCUIT PROTECT. electronic

INDUCTIVE LIMIT

TRIPPING VOLTAGE to Up + 1V RESIDUAL CURRENT 20 uA at 0 Signal

SIGNAL LEVEL

-AT 0 SIGNAL max. 3V

-AT 1 SIGNAL min. supply - 2,5V

Switching delay 15 us

### **EXTERNAL SYNCHRONIZATION VOLTAGE**

- RATED VALUE 15 V eff. - PERM. RANGE 10 to 20 V eff.

- LOADING 20 kOhm input impedance, Differential input

### **ANALOG OUTPUT**

- RANGE 0 - 10 V - ACCURACY 10 bit - RESOLUTION 12 bit

- OUTPUT CURRENT 20 mA protected against short circuit

# 6. Pin Allocation of the PG26

## 6.1.Pin Allocation of the Serial Interface X01

| PIN | V 24                    |       | 20 mA (TTY)             |      |

|-----|-------------------------|-------|-------------------------|------|

| 1   | FRAME GROUND            |       | FRAME GROUND            |      |

| 2   | TRANSMIT DATA OUT       | T*D   |                         |      |

| 3   | RECEIVE DATA IN         | R*D   |                         |      |

| 4   | REQUEST TO SEND OUT     | *RTS  |                         |      |

| 5   | CLEAR TO SEND           | *CTS  |                         |      |

| 6   | DATA SET READY IN       |       |                         |      |

| 7   | GROUND                  |       |                         |      |

| 8   | DATA CARRIER DETECT IN  | *DCD  |                         |      |

| 9   | GROUND                  |       | GROUND                  |      |

| 10  |                         |       | CURRENT LOOP + TRANSMIT | +T*D |

| 11  | +15 V                   |       | +15 V                   |      |

| 12  |                         |       | 20 MA SOURCE 1          |      |

| 13  |                         |       | CURRENT LOOP + RECEIVE  | +R*D |

| 14  |                         |       | CURRENT LOOP - RECEIVE  | -R*D |

| 15  | RECEIVE/TRANSMIT CLOCK  | *RT*C |                         |      |

| 16  |                         |       | 20 MA SOURCE 2          |      |

| 17  | RECEIVE/TRANSMIT CLOCK  |       |                         |      |

| 18  | GROUND                  |       | GROUND                  |      |

| 19  |                         |       | CURRENT LOOP - TRANSMIT | -T*D |

| 20  | DATA TERMINAL READY OUT |       |                         |      |

| 21  |                         |       | 20 MA DRAIN 2           |      |

| 22  | +5 V                    |       | +5 V                    |      |

| 23  | +5 V                    |       | +5 V                    |      |

| 24  | TRANSMIT RECEIVE CLOCK  | *TR*C | 20 MA DRAIN 1           |      |

| 25  | -15 V                   |       | -15 V                   |      |

# 6.2. Pin Allocation of the External Signals X5

| PIN | Designation                                                      |

|-----|------------------------------------------------------------------|

| 1   | External synchronization voltage                                 |

| 2   | Reference voltage to pin 1                                       |

| 3   | P15 Output, 15 V                                                 |

| 4   | External pulse disable connected via switch to pin 3             |

|     | jumpered = pulses enabled                                        |

|     | open or 0V = pulses disabled                                     |

| 5   | Synchronization of the pulse chains, connected with further PG's |

|     | Output voltage 'H' 10V - 14 V                                    |

|     | Output current, max. 'H' 40 mA                                   |

| 6   | Analog current actual value ±10 V, Ri = 2.2kOhm                  |

| 7   | Excitation current setpoint 010V, Ri = 2.2kOhm                   |

| 8   | Ground (digital), reference voltage                              |

| 9   | Summated pulses as in X 15                                       |

| 10  | Display zero indication of synchronization voltage               |

|     | Logic level 15 V, Ri = 2,2kOhm for H-Signal                      |

# 6.3. Pin Allocation of the Binary inputs and outputs X6

| PIN | Designation                                 |

|-----|---------------------------------------------|

| 1   | Binary input 1                              |

| 2   | Binary input 2                              |

| 3   | Binary input 3                              |

| 4   | Binary input 4                              |

| 5   | Binary output 1                             |

| 6   | Binary output 2                             |

| 7   | Binary output 3                             |

| 8   | Binary output 4                             |

| 9   | P ext. input                                |

|     | Supply voltage for binary outputs max. 30 V |

| 10  | M ext. input                                |

# 6.4. Pin Allocation of the SITOR Interface X7M, X7S

The allocation of both interfaces is identical, the signals marked with an '\*' are not utilized or generated at X7S.

| DIN | Da | oi en otio e                                                 |

|-----|----|--------------------------------------------------------------|

| PIN | De | signation Shield                                             |

| 1   |    |                                                              |

| 2   |    | Shield                                                       |

| 3   |    | Fuse monitor (fault = "L")                                   |

| 4   |    | Shield                                                       |

| 5   |    | Voltage zero (L1-L3)                                         |

| 6   |    | Shield                                                       |

| 7   | *  | $\pm$ I (actual) Frequency 60 $\pm$ 30 kHz $\pm$ 2 I (N)     |

| 8   | *  | Reference voltage excitation current setpoint                |

| 9   |    | External M24 ground                                          |

| 10  |    | PULSE 1.6                                                    |

| 11  |    | External M24 ground                                          |

| 12  |    | PULSE 1.3                                                    |

| 13  |    | Shield                                                       |

| 14  |    | External M24 ground                                          |

| 15  |    | PULSE 2.4                                                    |

| 16  |    | External M24 ground                                          |

| 17  |    | PULSE 2.1                                                    |

| 18  |    | U/SYN (Synchronization voltage) (STAR POINT)                 |

| 19  | *  | I = 0 message excitation (I = 0 = "H")                       |

| 20  |    | Temperature monitor (fault = "L")                            |

| 21  |    | Shield                                                       |

| 22  | *  | $\pm U(A)$ actual frequency 60 $\pm$ 30 kHz = $\pm U(AN)$    |

| 23  |    | Shield                                                       |

| 24  | *  | $\pm$ I(act) analog $\pm$ 10 V = $\pm$ I(N), not with SE20.2 |

| 25  |    | Shield                                                       |

| 26  |    | External M24 ground                                          |

| 27  |    | PULSE 1.4                                                    |

| 28  |    | External M24 ground                                          |

| 29  |    | PULSE 1.1                                                    |

| 30  |    | PULSE 2.2                                                    |

| 31  |    | External M24 ground                                          |

| 32  |    | PULSE 2.5                                                    |

| 33  |    | External M24 ground                                          |

| 34  |    | U/SYN (L1)                                                   |

| 35  |    | Undervoltage monitor (fault = "L")                           |

| 36  |    | Shield                                                       |

| 37  |    | zero voltage transgression (L1 - L2)                         |

| 38  |    | Shield                                                       |

| 39  |    | I = 0-Message $(I = 0 = "H")$                                |

| 40  |    | Shield                                                       |

| 41  | *  | Excitation current setpoint (0 - 10V)                        |

| 42  |    | PULSE 1.2                                                    |

| 43  |    | External M24 ground                                          |

| 44  |    | PULSE 1.5                                                    |

| 45  |    | External M24 ground                                          |

| 46  |    | External M24 ground                                          |

| 47  |    | PULSE 2.6                                                    |

| 48  |    | External M24 ground                                          |

| 49  |    | PULSE 2.3                                                    |

| 50  |    | Shield                                                       |

|     |    |                                                              |

## 6.5. Allocation of the Measurement Jacks X10 - X15

| X10 | Reference point ( Ground ) for | all other measurement jacks |

|-----|--------------------------------|-----------------------------|

| X11 | Board reset when jumpered to   | X10                         |

| X12 | Line voltage L1-L3             | (0-24 V)                    |

| X13 | analog current actual value    | (± 10 V)                    |

| X14 | Summated pulses slave          | (0-15 V)                    |

| X15 | Summated pulses master         | (0-15 V)                    |

All measurement values are digital except the signal on X13 . Ri each 2,2kOhm

# 6.6. Power converter specific signals X200

| Pin-No. | Signal           | Pin-No. | Signal                      |

|---------|------------------|---------|-----------------------------|

| 1       | Ground           | 26      | Slave Pulse 2.6             |

| 2       | P5               | 27      | Pulse disable Master        |

| 3       | Master pulse 1.1 | 28      | Q12 stepping signal         |

| 4       | Master pulse 1.2 | 29      | Slave frequency fU          |

| 5       | Master pulse 1.3 | 30      | Reset                       |

| 6       | Master pulse 1.4 | 31      | Pulse disable               |

| 7       | Master pulse 1.5 | 32      | SYN1 Master                 |

| 8       | Master pulse 1.6 | 33      | SYN1 Slave                  |

| 9       | Master pulse 2.1 | 34      | Fault Master/Slave          |

| 10      | Master pulse 2.2 | 35      | Fault RH rotating field     |

| 11      | Master pulse 2.3 | 36      | Fault free                  |

| 12      | Master pulse 2.4 | 37      | Summated fault SITOR        |

| 13      | Master pulse 2.5 | 38      | Master temperature monitor  |

| 14      | Master pulse 2.6 | 39      | Master fuse monitor         |

| 15      | Slave pulse 1.1  | 40      | Master fault excit. current |

| 16      | Slave pulse 1.2  | 41      | Master fault undervoltage   |

| 17      | Slave pulse 1.3  | 42      | current zero message M or S |

| 18      | Slave pulse 1.4  | 43      | Slave L13                   |

| 19      | Slave pulse 1.5  | 44      | Slave L12                   |

| 20      | Slave pulse 1.6  | 45      | Slave temperature monitor   |

| 21      | Slave pulse 2.1  | 46      | Slave fuse monitor          |

| 22      | Slave pulse 2.2  | 47      | Ground                      |

| 23      | Slave pulse 2.3  | 48      | Slave fault undervoltage    |

| 24      | Slave pulse 2.4  | 49      | Ground                      |

| 25      | Slave pulse 2.5  | 50      | P5                          |

All signals 5V level

# 6.7. Switch set-ups S1-S4

S1 Right hand rotating field X7S monitor

open : active jumpered : disabled

S2 Slave-Line lag monitor

open : active jumpered : disabled

S3 Pulse sample reset at X7S

open : active for 12 pulse operation

jumpered: disabled, pulses at X7M and X7S identical

S4 always open, used for internal checks

# 7. Mask of the PG26 in the Master Program

| : PG26       | "Processor board Direct Current 1, L-Bus" |

|--------------|-------------------------------------------|

| PIJ 1N = 0   | "Interrupt processing FP"                 |

| SFJ 1N = 0   | "System error FP"                         |

| PRX 1N = 0   | "Special communication FP receive"        |

| PJ1 1N = ?   | "1. Permanent processing FP"              |

| PJ2 1N = 0   |                                           |

| PJ3 1N = 0   |                                           |

| PJ4 1N = 0   |                                           |

| PJ5 1N = 0   |                                           |

| PJ6 1N = 0   |                                           |

| PJ7 1N = 0   |                                           |

| PJ8 1N = 0   |                                           |

| PTX 1N = 0   | "Special communications FP transmit"      |

| ILS IK = 0   | "L Bus interrupt transmit"                |

| T0 TG = ?    | "Basic clock rate"                        |

| T1 TS = ?    | "1.Clkr.*T0,generated LB conn."           |

| T2 TS = ?    | "2.Clkr. " "                              |

| T3 TS = ?    | "3.Clkr. " "                              |

| T4 TS = ?    | "4.Clkr. " "                              |

| T5 TS = ?    | "5.Clkr. " "                              |

| TY TX = T?   | "System FP clock rate"                    |

| SSM $2C = 0$ | "Length save area, (n*1+2) kByte"         |

| ISE 1C = N   | "Ignore failed message (RDYINT) (Y/N)?"   |

| CCT 8R = 0   | "Transmit communication name.Tx"          |

| CCR 8R = 0   | "receive communication name.Tx"           |

| COP 8R = 0   | "Dialog communication name.Tx"            |

| CMS $8N = 0$ | "Message system name"                     |

| CTS 8N = 0   | "Transport system name"                   |

| MS 2M = 0    | "Message system"                          |

| X6A 4K <     | "Binary inputs, interrupt"                |

| X7A 1K <     | "Current actual value (SITOR)"            |

| X7B 1K <     | "EMF (SITOR)"                             |

| X7E 4K <     | "Monitor watchdog (SITOR)"                |

| X6B 4K >     | "Binary outputs"                          |

| X7C 1K <     | "Controller set (SITOR)"                  |

| X7D 1K <     | "Command module (SITOR)"                  |

| X7F 1K <     | "Analog output (SITOR)"                   |

| ++++++++++++ | ***************************************   |

|              |                                           |

PG26 requires 1 Sub-module

Allocation of plugs and function modules

The SITOR connector can be accessed by the following function modules:

## CONNECTOR SECTION FUNCTION MODULE

| X6A BII8 | Binary input  | (4 Binary values) |

|----------|---------------|-------------------|

| X6B BIQ8 | Binary output | (4 Binary values) |

Use of the BII8 module on the PG26 requires paying attention to the fact that the four highest bits can take on undefined values. They should be filtered out.

| X7A | CAV   | Current actual value    | (SITOR) |

|-----|-------|-------------------------|---------|

| X7B | EMF   | EMF                     | (SITOR) |

| X7C | Tgxxx | Controller stage        | (SITOR) |

| X7D | SOL   | Command stage           | (SITOR) |

| X7E | TGF   | Watchdog, fault detect. | (SITOR) |

| X7A | FCS   | Analog output           | (SITOR) |

# 8. Appendices

# 8.1. Block diagram

Block diagram 3SE 465 601 9005.00 SU

## 8.2. Scale drawing and table of the plug connector

Scale drawing with view of front panel and table of the

implemented plug connector 3SE 465 601 9005.00 MB

## 8.3. Allocation plan

Allocation plan 3SE 465 601 9005.00 AO

## 8.4. Scale drawing of the cable for special lengths

Scale drawing with order numbers for manufacturing cables with special lengths

3GE 465 684 9000.11 MB

## 9. Miscellaneous

## 10. ECB instructions

Components which can be destroyed by electrostatic discharge (ECB)

Generally, electronic boards should only be touched when absolutely necessary.

The human body must be electrically discharged before touching an electronic board. This can be simply done by touching a conductive, grounded object directly beforehand (e.g. bare metal cubicle components, socket outlet protective conductor contact.

Boards must not come into contact with highly-insulating materials - e.g. plastic foils, insulated desktops, articles of clothing manufactured from man-made fibers.

Boards must only be placed on conductive surfaces.

When soldering, the soldering iron tip must be grounded.

Boards and components should only be stored and transported in conductive packaging (e.g. metalized plastic boxes, metal containers).

If the packing material is not conductive, the boards must be wrapped with a conductive packing material, e.g. conductive foam rubber or household aluminum foil.

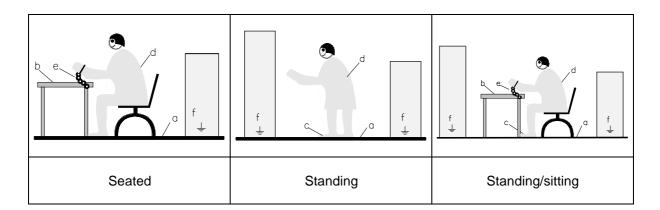

The necessary ECB protective measures are clearly shown in the following diagram.

a = Conductive floor surface

b = ECB table

c = ECB shoes

d = ECB overall e = ECB chain

f = Cubicle ground connection

18

Drives and Standard Products Motors and Drives Systems Group Postfach 3269, D-91050 Erlangen