# SIEMENS

Technical Description Order number: 6AR1930-4AA06-2AA0

April 2003

## **SMP16-SFT251**

Order number: 6AR1304-0EA00-0AA0

Counter board with two 32-bit incremental/pulse counters

**SICOMP Industrial Microcomputer**

(4)J31069-D2090-U001-A1-7618

#### **Product History of the Technical Description**

| Revision <sup>1)</sup> | Record of Changes                                 | Date  |

|------------------------|---------------------------------------------------|-------|

| A0                     | First edition                                     | 03/00 |

| A1                     | Control Register 1 and 2, Chapter 6.4.3 and 6.4.4 | 04/03 |

1) Corresponds to the 4th block of digits of the drawing number in the footer

#### **Explanation of Notation**

- \* An asterisk behind the signal name indicates a low-active signal (e.g., IOR\*).

- A slash between two signal names separates two level-dependent functions of one signal.

Example: C/D\* means Command for high level and Data for low level.

- x Bits marked with an x in the register descriptions are irrelevant.

- Connections indicated with a dash in a connector assignment table are reserved (i.e., bus or I/O interface).

- **Signal** Special signals not included in these specifications are indicated in bold print in the signal assignment tables and then explained (e.g., **AMSEOP**).

Notes:

SICOMP® is a registered trademark of Siemens AG.

IBM AT® and IBM PC® are registered trademarks of the International Business Machines Corp.

INTEL® is a registered trademark of the INTEL Corp.

MS-DOS®, Windows® and Windows NT® are registered trademarks of Microsoft.

All other designations used in this documentation may be trademarks whose use by third parties for their own purposes may violate the rights of the owner.

Passing on and reproduction of this document, as well as utilization and communication of its contents is prohibited unless expressly authorized. Offenders will be liable for damages. All rights reserved, particularly in the event a patent is granted or a utility model is registered.

No responsibility is assumed for circuits, descriptions and tables contained in this document concerning freedom from rights of third parties. Information in the technical descriptions specifies products but does not guarantee characteristics. The product described in this documentation may require licensing. Questions should be directed to your local Siemens office.

Availability and technical modifications subject to change without prior notice.

ES43/Kt/WW8.0/VS5.0/A4

## Safety Notes for SICOMP Boards

#### **ESD** protection measures

#### Caution

When handling boards and other components carrying this symbol, always adhere to ESD protection guidelines (Electrostatic **S**ensitive **D**evices).

- Never touch the boards unless required work makes this absolutely necessary.

- When working with the boards, use a conductive and grounded work surface.

- Wear a grounding bracelet.

- Never touch the pins, connections or printed circuits of the boards.

- Never permit the boards or components to be touched by chargeable objects (e.g., synthetic materials).

- Keep the boards or components at least 10 cm away from CRT units and television sets.

- Leave the boards in their special packaging until they are needed. When registering boards, etc. do not remove the boards from their packaging or touch them.

- Boards may only be installed or removed when the voltage is off.

#### Wiring of Bus Backplanes

System-related signal wiring on SICOMP board systems is performed with wrap connections. The power supply cables are bundled together with cable binders. These cables are equipped with plug-in or screw connections.

#### **Caution:**

All signal wiring (the interrupt signal lines in particular) must be of the appropriate design and kept as short as possible. When longer interrupt signal lines cannot be avoided, twisted pair wiring must be used.

#### **Related SICOMP SMP16 Literature**

For more information on installing and handling SICOMP boards, see "SICOMP IMC system manual".

## **Table of Contents**

| 1 | Initial \$                                                                                        | Startup                                                                                                                                                                                                                                                                                                  | 7                                            |

|---|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   | 1.1                                                                                               | Preparing for Software Configuration                                                                                                                                                                                                                                                                     | 7                                            |

|   | 1.2                                                                                               | Wiring the I/O                                                                                                                                                                                                                                                                                           | 9                                            |

| 2 | Featur                                                                                            | es                                                                                                                                                                                                                                                                                                       | 10                                           |

|   | 2.1                                                                                               | Characteristics                                                                                                                                                                                                                                                                                          | 10                                           |

|   | 2.2                                                                                               | Front LEDs                                                                                                                                                                                                                                                                                               | 11                                           |

|   | 2.3                                                                                               | Operational Values                                                                                                                                                                                                                                                                                       | 12                                           |

|   | 2.4                                                                                               | Physical Characteristics of the Encoder Signals                                                                                                                                                                                                                                                          | 13                                           |

|   | 2.5<br>2.5.1<br>2.5.2<br>2.5.3                                                                    | Time Requirements for the Input Signals<br>Encoder Signals<br>Frequency and Pulse Width Measurement<br>Special Signals                                                                                                                                                                                   | 13<br>13<br>14<br>14                         |

|   | 2.6                                                                                               | Time Relationships of the 24 V Interface                                                                                                                                                                                                                                                                 | 15                                           |

|   | 2.7                                                                                               | Ambient Conditions                                                                                                                                                                                                                                                                                       | 16                                           |

|   | 2.8                                                                                               | Recommended Accessories                                                                                                                                                                                                                                                                                  | 16                                           |

| 3 | Interfa                                                                                           | ces                                                                                                                                                                                                                                                                                                      | 17                                           |

|   | 3.1                                                                                               | Overview of the Interfaces                                                                                                                                                                                                                                                                               | 17                                           |

|   | 3.2<br>3.2.1<br>3.2.2                                                                             | Pin Connector X2 to SMP16 Bus<br>Signals for the Daisy Chain<br>Other Special Signals                                                                                                                                                                                                                    | 18<br>18<br>19                               |

|   | 3.3                                                                                               | I/O Connectors X3 and X4                                                                                                                                                                                                                                                                                 | 20                                           |

|   | 3.4                                                                                               | Interface Switches S1 and S2                                                                                                                                                                                                                                                                             | 21                                           |

| 4 | Config                                                                                            | uration with Software                                                                                                                                                                                                                                                                                    | 22                                           |

| 5 | Compa                                                                                             | atibility with SMP-E251                                                                                                                                                                                                                                                                                  | 24                                           |

| 6 | Progra                                                                                            | Imming the Board                                                                                                                                                                                                                                                                                         | 25                                           |

|   | 6.1                                                                                               | Register Overview                                                                                                                                                                                                                                                                                        | 25                                           |

|   | 6.2                                                                                               | Reset Reactions                                                                                                                                                                                                                                                                                          | 28                                           |

|   | $\begin{array}{c} 6.3 \\ 6.3.1 \\ 6.3.2 \\ 6.3.3 \\ 6.3.4 \\ 6.3.5 \\ 6.3.6 \\ 6.3.7 \end{array}$ | Function Description<br>Reading the Counter Status<br>Loading the Counters<br>Position Acquisition via Shaft Encoder Edge Evaluation<br>Position Acquisition with Hardware Support<br>Position Acquisition without Hardware Support<br>Frequency and Pulse Width Measurement<br>Overview of the Commands | 29<br>29<br>29<br>30<br>32<br>33<br>35<br>38 |

| 6.3.8           | Extra Inputs ZS00 to ZS30 (Counting Channel 0) or ZS01 to ZS31 (Counting                                              | 10       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|----------|

| 6.3.9           | Channel 1)<br>The Universal Registers                                                                                 | 40<br>40 |

| 6.3.10          | The Clear Functions                                                                                                   | 40       |

| 6.3.11          | The Hysteresis Functions                                                                                              | 42       |

| 6.3.12          | Switching the Two Counting Channels in Parallel                                                                       | 43       |

| 6.3.13          | Interrupts                                                                                                            | 43       |

| 6.4             | Description of the Registers                                                                                          | 44       |

| 6.4.1           | Mode Registers, Channel 0 and Channel 1                                                                               | 44       |

| 6.4.2           | Control Register 0                                                                                                    | 45       |

| 6.4.3           | Control Register 1 (16-Bit Register, Addresses x and x+1)                                                             | 46       |

| 6.4.4           | Control Register 2 (16-Bit Register, Addresses x+2 and x+3)                                                           | 47       |

| 6.4.5           | Interrupt Mask (16-Bit Register, Addresses x+4 and x+5)                                                               | 49       |

| 6.4.6           | Interrupt Register, Channel 0 and Channel 1                                                                           | 50       |

| 6.4.7           | Status Register 0                                                                                                     | 51       |

| 6.4.8           | Status Register 1<br>Status Register 2 (16 Bit Register, Addresses v. 6 and v. 7)                                     | 52<br>53 |

| 6.4.9<br>6.4.10 | Status Register 2 (16-Bit Register, Addresses x+6 and x+7)<br>Clear Register (16-Bit Register, Addresses x+6 and x+7) | აა<br>55 |

|                 |                                                                                                                       |          |

| 6.5             |                                                                                                                       | 57       |

| 6.5.1           | Read/Write Accesses                                                                                                   | 57       |

| 6.5.2           | Board Commands                                                                                                        | 57       |

| Sample          | e Programs                                                                                                            | 58       |

| 7.1             | Position Acquisition with Hardware Support (BG_Mode = "0")                                                            | 58       |

| 7.2             | Position Acquisition without Hardware Support (BG_Mode = "1")                                                         | 60       |

| 7.3             | Frequency and Pulse Width Measurement without Using the Zero-Marking-                                                 |          |

|                 | Pulse Input                                                                                                           | 61       |

7

## 1 Initial Startup

The primary steps involved in the initial startup of the board are listed below.

1. Software configuration. See chapters 1.1 and 4 for more information.

#### Attention:

Chip select channel 0 must be **enabled** for the board. The other channels can be enabled or disabled depending on the particular application. The ASBIC channel must be **disabled**.

2. Wiring I/O devices. See chapter 1.2 or 2.8 for more information.

## 1.1 Preparing for Software Configuration

The configuration of the board with the SMP16-AKO auto configuration software (see chapter 2.8) can be performed directly in the target system or in a separate generation system. In addition, the configuration can be performed in a separate system, but the board can still be configured in the target system.

In all cases, the board must be installed in an SMP16 bus system with daisy chain connection at the time of programming.

#### Configuration in the target system

|                   | Requirements on the Target System    |  |

|-------------------|--------------------------------------|--|

| Required hardware | SICOMP IMC AT CPU                    |  |

|                   | SMP16 bus backplane with daisy chain |  |

| Required software | Windows 95                           |  |

|                   | • SMP16-AKO V2.0                     |  |

# Configuration in the target system, generation of the configuration in separate system

|                                 | Requirements on the Target System                                                   | Requirements on the Generation<br>System                           |  |

|---------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Required hardware <sup>1)</sup> | <ul> <li>SICOMP IMC AT CPU</li> <li>SMP16 bus backplane with daisy chain</li> </ul> | <ul> <li>PC-AT (e.g., workplace computer or<br/>laptop)</li> </ul> |  |

| Required software               | <ul><li> RMOS or MS-DOS</li><li> AKO start program</li></ul>                        | <ul><li>Windows 95 or Windows NT</li><li>SMP16-AKO V2.0</li></ul>  |  |

1) In addition, there must be a way to transfer the generated configuration file (i.e., STARTUP.SKD) to the target system. Some examples are listed below.

- Serial connection via zero modem cable (is supported by AKO start program)

- Floppy disk drives on both systems

- LAN connection

### Configuration in a separate generation system

The board is installed in the generation system for configuration and then returned to the target system afterwards.

|                   | Requirements on the Generation System |  |

|-------------------|---------------------------------------|--|

| Required hardware | SICOMP IMC AT CPU                     |  |

|                   | SMP16 bus backplane with daisy chain  |  |

| Required software | Windows 95                            |  |

|                   | SMP16-AKO V2.0                        |  |

#### Daisy chaining for configuration via software

With SMP16-SYS403 bus backplanes with 5 or more slots, the daisy change connection is already implemented electronically.

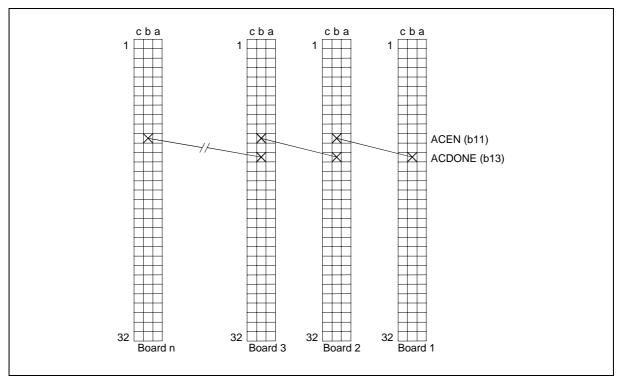

With the other bus backplanes, the slots of the software-configurable boards must be wired as shown below.

Figure 1.1 Daisy chaining on the SMP16 bus backplane for configuration via software

The ACEN input of the first software configurable board in the chain of configuration remains open as does the ACDONE output of the last board. All other ACDONE outputs must be connected with the ACEN input of the next board. See chapter 3.2.1.

## 1.2 Wiring the I/O

The differential control lines must be twisted in pairs (see chap. 3.3). The single-ended control lines must be twisted with the related ground.

The shield must be applied (for HF) to both the board and the addressed I/O. To prevent equalizing currents on the shield, an equipotential bonding conductor should be installed parallel to the signal line.

Never install your control lines near strong interference (e.g., motors, relays, high-voltage or power lines, thyristor controllers, power inverters and transmitters).

Also adhere to the information on electromagnetic compatibility contained in the SICOMP IMC system manual under the chapter on ambient conditions.

## 2 Features

### 2.1 Characteristics

The SMP16-SFT251 is a counter board with two 32-bit counters. Its software is compatible with the SMP-E251. It should be used instead of the SMP-E251.

The board has the following characteristics.

#### General

- Two 15-pin, sub D socket strips for connection of the I/O

- Free-convection ventilation

- EEPROM for identification and parameterization of the board

- Automatic configuration with "auto configuration" (see chap. 4)

- 5 V encoder power drawn from bus voltage (via fuse)

#### **Functions per channel**

- Position acquisition with connection of a two-track incremental encoder (single, double or quadruple edge evaluation, max. track frequency of 2 MHz)

- One zero-marking-pulse latch register and 3 extra latch registers (can be triggered by digital inputs) one of which can also be used as a comparator register

- Three digital, single-ended inputs (24 V) for triggering the extra latch registers or for generating interrupts

- One digital, single-ended input (24 V) for resetting the counter or for triggering interrupts

- A comparator register can be used to trigger an alarm (interrupt, status bit) when a certain counter state is reached and/or to reset the counter.

- Both the shaft encoder signals and the digital inputs of channel 0 can be assigned to channel 1. This makes it possible to run both counters parallel to each other.

- Frequency or pulse width measurement with frequencies up to 4 MHz. Either level or edgecontrol can be used to start the counter.

- The counting signals (A track and B track) and the zero marking pulse (N track) can be set with DIP switches for either 24 V technology or for RS 422.

- The operating modes can be set separately for each channel.

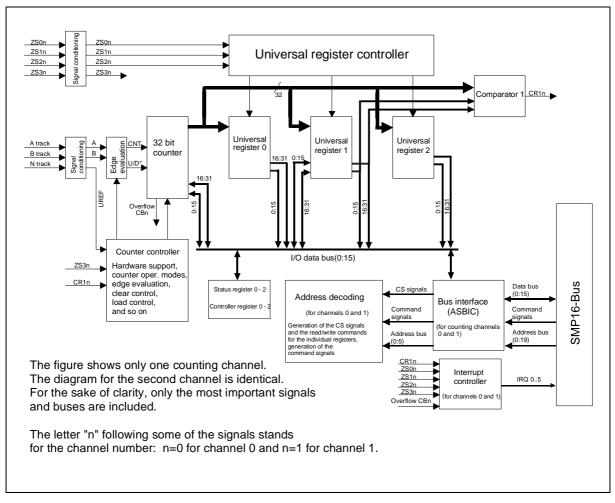

The following block circuit diagram shows the logical organization of the board.

Figure 2.1 Block circuit diagram of the SMP16-SFT251

### 2.2 Front LEDs

The two front LEDs (L1 and L2) show the direction of rotation of the shaft encoder for channel 0 or channel 1 during position acquisition.

These LEDs are irrelevant for "frequency and pulse width measurement" mode.

| Cha | ann | el | 0: |

|-----|-----|----|----|

|     |     |    |    |

| Direction of Rotation | Status - LED L1 |

|-----------------------|-----------------|

| Up                    | On              |

| Down                  | Off             |

#### Channel 1:

| Direction of Rotation | Status - LED L2 |

|-----------------------|-----------------|

| Up                    | On              |

| Down                  | Off             |

## 2.3 Operational Values

| System portion                                                   |                                                                                                                          |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Voltage supply (from SMP16 bus)                                  | +5 V ±5%                                                                                                                 |

| Current consumption with nominal voltage (without encoder power) | Max. of 400 mA                                                                                                           |

| Counter inputs                                                   |                                                                                                                          |

| Number of channels                                               | 2                                                                                                                        |

| Counter size                                                     | 32 bits                                                                                                                  |

| Interfaces: encoder inputs A, B, and N (zero marking pulse)      | 24 V technology, opto-decoupled<br>(single-ended or differential)<br>or RS 422                                           |

| Operational values with 24 V technology:                         |                                                                                                                          |

| Differential                                                     | ±13 V to ±30 V                                                                                                           |

| Differential, max. ratings                                       | ±34 V                                                                                                                    |

| Single-ended, low level                                          | –3 V to +5 V                                                                                                             |

| Single-ended, high level                                         | +13 V to +30 V                                                                                                           |

| Single-ended, max. ratings                                       | ±34 V                                                                                                                    |

| Input current with 24 V technology $(U_{in} = 24 V)$             | 11.4 mA (typ.)                                                                                                           |

| (U <sub>in</sub> = 30 V)                                         | 15.1 mA (max.)                                                                                                           |

| See RS 422 specifications for operational values with RS 422.    |                                                                                                                          |

| Input frequency for incremental encoders:                        | 2 MHz (max.)                                                                                                             |

| Input frequency with frequency/gate time measurement             | 4 MHz (max.)                                                                                                             |

| Extra inputs                                                     |                                                                                                                          |

| Number                                                           | 4 per channel                                                                                                            |

| Interfaces                                                       | 24 V technology                                                                                                          |

| Input voltage, low level                                         | –3 V to +5 V                                                                                                             |

| Input voltage, high level                                        | +13 V to +30 V                                                                                                           |

| Input voltage, max. ratings                                      | ±34 V                                                                                                                    |

| Input current with high level $(U_{in} = 24 V)$                  | 11.4 mA (typ.)                                                                                                           |

| (U <sub>in</sub> = 30 V)                                         | 15.1 mA (max.)                                                                                                           |

| 5 V encoder power                                                |                                                                                                                          |

| Encoder voltage                                                  | 5 V (typ.)<br>Depends on the power supply of the<br>SMP16 system and the voltage drops on<br>the board (typically 0.2 V) |

| Total current                                                    | 720 mA (max.)                                                                                                            |

| Short-circuit immunity                                           | Yes (with SMD safety fuse)                                                                                               |

### Notes on 24 V interface

The 24 V interface offers extra immunity to interference. The physical characteristics of this interface (high voltage swings with currents > 10 mA) restrict its use with high-speed applications. For this reason, encoders with the RS 422 interface should be used for encoder applications with track frequencies > 500 kHz. Otherwise, the encoder signals might not be transferred accurately which would cause counting errors in the system.

## 2.4 Physical Characteristics of the Encoder Signals

Encoders can be connected to the board with an RS 422 or 24 V interface. The desired physical characteristics must be selected with the two DIP switches (S1 and S2) on the board. See chapter 3.4.

#### Caution

Since setting the wrong interface may destroy the board, make sure that all DIP switches required for selection of the interface are set correctly.

## 2.5 Time Requirements for the Input Signals

### 2.5.1 Encoder Signals

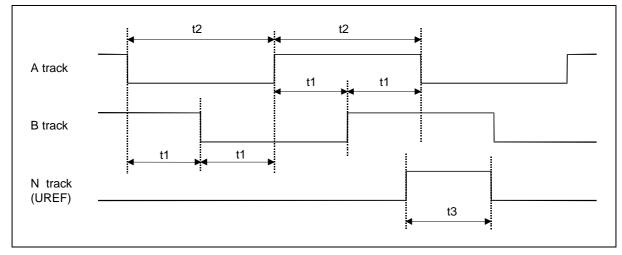

The two track signals (A and B) of the encoder must be displaced by 90° to each other.

Figure 2.2 Time relationships of the encoder signals

| t1 | A edge to B edge       | 125 nsec (min.) |

|----|------------------------|-----------------|

| t2 | Pulse width, A/B track | 250 nsec (min.) |

| t3 | Pulse width, N track   | 125 nsec (min.) |

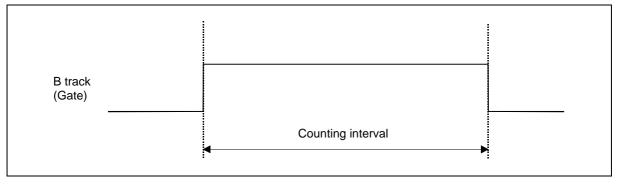

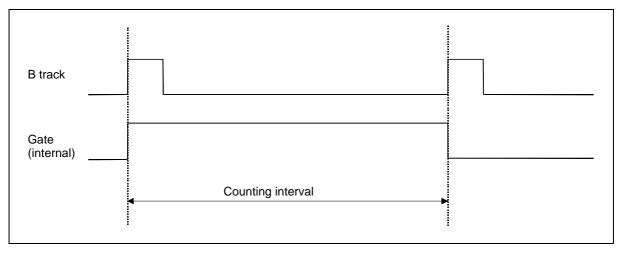

### 2.5.2 Frequency and Pulse Width Measurement

With frequency and pulse width measurement, the reference gate signal must be at least twice as long as the maximum expected cycle duration of the frequency to be measured.

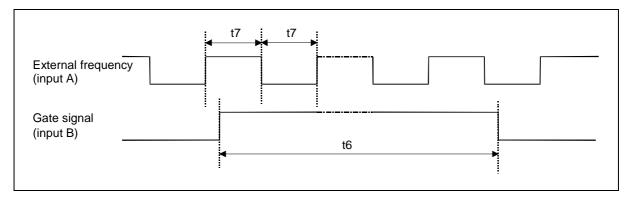

Figure 2.3 Time relationships with frequency and pulse width measurement

| t7 | Clock pulse high/low time                         | 125 nsec (min.) |

|----|---------------------------------------------------|-----------------|

| t6 | Gate time when the external clock pulse is used   | 2 x t7 (min.)   |

| t6 | Gate time when the internal clock pulses are used | t8 (min.)       |

| t8 | Cycle time of the internal clock pulses:          |                 |

|    | 1.25 MHz                                          | 800 nsec        |

|    | 2.5 MHz                                           | 400 nsec        |

|    | 2.0 MHz                                           | 500 nsec        |

|    | 4.0 MHz                                           | 250 nsec        |

### 2.5.3 Special Signals

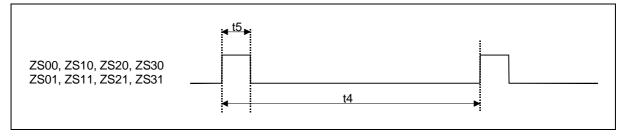

Figure 2.4 Time relationships of the special signals

| t4 | High edge to high edge | 400 nsec (min.) |

|----|------------------------|-----------------|

| t5 | Pulse width            | 250 nsec (min.) |

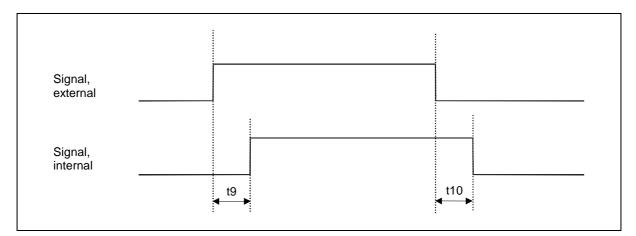

### 2.6 Time Relationships of the 24 V Interface

The following signal runtimes apply to the 24 V interface.

Figure 2.5 Signal runtimes for the 24 V interface

| t9  | Time from Low $\rightarrow$ High | 500 nsec (typ.) |

|-----|----------------------------------|-----------------|

| t10 | Time from High $\rightarrow$ Low | 400 nsec (typ.) |

These signal runtimes apply to 24 V outputs with push-pull clock pulse technology. Other runtimes may apply when other technologies are used.

## 2.7 Ambient Conditions

|                                                                                                   | Operation                                                                                                |                            | Transportation and Storage                       |                            |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------|----------------------------|

| Temperature                                                                                       | 0° C to 55° C                                                                                            |                            | –40° C to +70° C                                 |                            |

| Relative humidity (RH)                                                                            | 10% to 90%                                                                                               |                            | 10% to 90%                                       |                            |

| Permissible air pressure                                                                          | 450 hPa to 1100 hPa                                                                                      |                            |                                                  |                            |

| Permissible temperature fluctuation                                                               | 10° C/30 min. (without condensation) or 0.5° C/min.                                                      |                            |                                                  | C/min.                     |

| Vibrations<br>in acc. w. IEC 68-2-6 Test FC,<br>20 cycles in 3 axes,<br>approx. 11 min. per cycle | 10 Hz to 61 Hz:<br>61 Hz to 500 Hz:                                                                      | 0.2 mm<br>amplitude<br>2 g | 5 Hz to 8 Hz:<br>8 Hz to 500 Hz:                 | 7.5 mm<br>amplitude<br>1 g |

| Shock                                                                                             | IEC 68-2-27 Test E/A<br>3 times per axis<br>2 directions per axis<br>total of 18 impacts<br>15 g/11 msec |                            | IEC 68-2-29<br>per 1000 impacts a<br>25 g/6 msec | at 6 levels                |

### 2.8 Recommended Accessories

**SMP16-AKO** Auto-configuration software for MS-DOS and Windows for setting the SMP16 bus interface

Order number: 6AR1400-0FA10-3AA0

The product includes online help with a detailed description of the function and handling of the configuration software.

The files (SFT251.BGB and SFT251.BGT) which are required to set the board are available on the Internet under: http://www.ad.siemens.de/sicomp/html\_76/hotline.htm

SMD safety fuse Order number: R451.750 (the Littlefuse company)

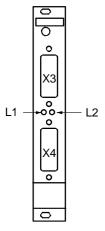

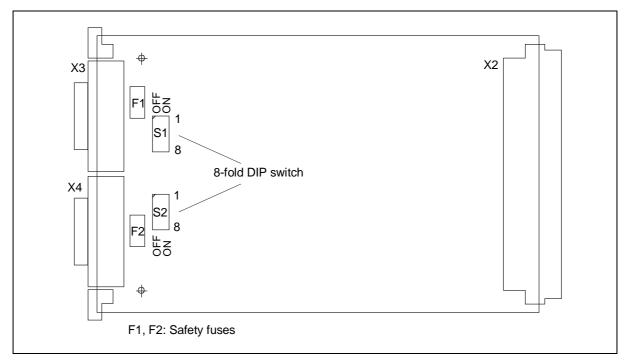

Figure 3.1 shows where the two fuses are located on the board.

## 3 Interfaces

### **3.1 Overview of the Interfaces**

| Pin | Design                             | Use                                                         |

|-----|------------------------------------|-------------------------------------------------------------|

| X1  | Socket strip, 20-pin               | Reserved                                                    |

| X2  | Multi-point terminal strip, 96-pin | SMP16 bus interface                                         |

| X3  | Sub D socket, 15-pin               | Input, counting channel 0                                   |

| X4  | Sub D socket, 15-pin               | Input, counting channel 1                                   |

| S1  | DIP switch, 8-pin                  | Switch, 24 V technology $\leftrightarrow$ RS 422, channel 0 |

| S2  | DIP switch, 8-pin                  | Switch, 24 V technology $\leftrightarrow$ RS 422, channel 1 |

Figure 3.1

Overview of the connection and setting elements

## 3.2 Pin Connector X2 to SMP16 Bus

The following table shows the bus signals used by the board.

| Pin | а        | b      | C         |

|-----|----------|--------|-----------|

| 1   | -        | A16    | _         |

| 2   | -        | A17    | GND       |

| 3   | -        | AEN    | +5 V      |

| 4   | -        | _      | MMIO*     |

| 5   | MEMCS16* | _      | A12       |

| 6   | RESET*   | _      | A0        |

| 7   | -        | _      | A13       |

| 8   | MEMR*    | _      | A1        |

| 9   | RESIN*   | _      | A14       |

| 10  | MEMW*    | _      | A2        |

| 11  | -        | ACEN   | A15       |

| 12  | RDYIN    | _      | A3        |

| 13  | BUSEN    | ACDONE | INT0oNMI* |

| 14  | DB0      | _      | A4        |

| 15  | -        | +5 V   | INT1*     |

| 16  | DB1      | GND    | A5        |

| 17  | -        | GND    | BS        |

| 18  | DB2      | _      | A6        |

| 19  | -        | _      | INT2*     |

| 20  | DB3      | _      | A7        |

| 21  | IOCS16*  | _      | INT3*     |

| 22  | DB4      | DB8    | A8        |

| 23  | -        | DB9    | INT4*     |

| 24  | DB5      | DB10   | A9        |

| 25  | -        | DB11   | INT5*     |

| 26  | DB6      | DB12   | A10       |

| 27  | -        | DB13   | INT0*     |

| 28  | DB7      | DB14   | A11       |

| 29  | -        | DB15   | NMI*      |

| 30  | IOW*     | BHEN   | IOR*      |

| 31  | -        | A18    | GND       |

| 32  | +5 V     | A19    | _         |

#### 3.2.1 Signals for the Daisy Chain

ACEN, Input (b11)

ACDONE Output, open collector (b13)

The ACEN input signals a board that it has been selected for configuration of the ASBIC chip. Using the ACDON output, it indicates that it has finished its own configuration and the next board can be configured. See chapter 1.1.

### 3.2.2 Other Special Signals

AEN Address Enable, input (b3)

Control signal for PC compatible bus accesses, must be connected with AEN (b3) to the CPU slot for PC-I/O addressing (up to 3FFh).

BS "Board Select," input, TTL level (c17) When low, this signal deactivates the board. However, the interrupts of the board still remain active.

#### Interrupts of the counting channels and extra inputs

| INT0*<br>INT1*<br>INT2*<br>INT3*<br>INT4*<br>INT5* | Interrupt output, open collector (c27)<br>Interrupt output, open collector (c15)<br>Interrupt output, open collector (c19)<br>Interrupt output, open collector (c21)<br>Interrupt output, open collector (c23)<br>Interrupt output, open collector (c25)                                                                                                                                                                                                                        |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT0oNMI*                                          | Interrupt output, open collector (c13)<br>Interrupt INT0* is located here so that it is compatible with the SMP-E251.<br>This interrupt is identical to the INT0* signal. Modern applications sometimes<br>use this pin as NMI*. When, for instance, the SMP16-COM595 bus coupler<br>and the SMP16-SFT251 are installed in the same slot for this reason, the<br>INT0* signal must be switched off from this pin. See chapter 6.4.5. INT0* can<br>always be taken from pin c27. |

| NMI*                                               | "Non Maskable Interrupt," output, open collector (c13)<br>Characteristics: low: 0.4 V/8 mA                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                    | Signalizes a hardware error of the ASBIC chipc or of the board.                                                                                                                                                                                                                                                                                                                                                                                                                 |

## 3.3 I/O Connectors X3 and X4

The following table shows the assignment of the 15-pin, sub D socket strips X3 and X4.

| Pin | Assignment | Pin | Assignment |

|-----|------------|-----|------------|

| 1   | VCC        | 9   | An         |

| 2   | VCC        | 10  | GND        |

| 3   | Bn*        | 11  | ZS1n       |

| 4   | An*        | 12  | ZS0n       |

| 5   | Nn         | 13  | ZS3n       |

| 6   | GND        | 14  | ZS2n       |

| 7   | Nn*        | 15  | GNDn       |

| 8   | Bn         |     |            |

n = Channel number (0 or 1)

| VCC                       | 5 V encoder power (via 750 mA fine fuse from the system power supply)                                                                          |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GND                       | Ground connection for shaft encoder signals                                                                                                    |  |

| An                        | Uninverted input of track A of channel n                                                                                                       |  |

| An*                       | Inverted input of track A of channel n                                                                                                         |  |

| Bn                        | Uninverted input of track B of channel n                                                                                                       |  |

| B0*                       | Inverted input of track B of channel n                                                                                                         |  |

| Nn                        | Uninverted input of track N of channel n                                                                                                       |  |

| Nn*                       | Inverted input of track N of channel n                                                                                                         |  |

| ZS0n, ZS1n,<br>ZS2n, ZS3n | Extra inputs for channel n (see chapter 6.3.8 for a description)                                                                               |  |

| GNDn                      | Ground connection for the extra inputs of channel n (summation point)<br>This ground can be connected to system ground (GND) with switch S1.8. |  |

#### Note:

The differential control lines (e.g., An and An\*) must be twisted in pairs.

When single-ended connection of a shaft encoder with a 24 V interface is to be used, the inverted inputs (An\*, Bn\* and Nn\*) of each signal (A, B, and N) must be connected to GND. The lines with the signals (An, Bn and Nn) must be twisted in pairs with the corresponding grounding line.

The lines of the extra inputs must be twisted in pairs with the corresponding grounding line.

## 3.4 Interface Switches S1 and S2

These two switches (S1 and S2) can be used to select the physical interface of the shaft encoder signals A, B and N for each channel. S1 is the selection switch for counting channel 0. S2 is the selection switch for counting channel 1.

|                    |                   | Counting Channel 1 |                   |  |

|--------------------|-------------------|--------------------|-------------------|--|

|                    |                   | 24 V technology    | RS 422            |  |

| S1.1 to S1.7 = OFF | S1.1 to S1.7 = ON | S2.1 to S2.7 = OFF | S2.1 to S2.7 = ON |  |

The two switches (S1.8 or S2.8) can be used to connect the grounding connection (GND0 or GND1) of the extra inputs of both counting channels to board ground.

| Counting Channel 0    | Counting Channel 1    |  |

|-----------------------|-----------------------|--|

| Connect GND0 with GND | Connect GND1 with GND |  |

| S1.8 = ON             | S2.8 = ON             |  |

#### Note:

This connection is provided for already existing applications with SMP-E251 for which pin 15 of plug connectors X3 and X4 was used as the grounding connection. In all other applications, this connection should be open.

## 4 Configuration with Software

The configuration data of the SMP16-SFT251 are stored by the ASBIC chip on the serial EEPROM of the board. The tables below show the default settings of the values which can be changed by the automatic configuration software SMP16-AKO.

#### Note:

The configuration data must be adjusted each time a system is changed by inserting or removing a board or module since the board or the module may not be able to be addressed otherwise.

#### Required settings in the "chip select channel 0 to 3" dialog fields

| Channel       | 0 (w)         | 1 (x)                 | 2 (y)                            | 3 (z)                            |

|---------------|---------------|-----------------------|----------------------------------|----------------------------------|

| Setting       | Enabled 1)    | Enabled <sup>1)</sup> | Enabled <sup>1)</sup>            | Enabled <sup>1)</sup>            |

| Address mode  | SMP-I/O       | SMP-I/O               | SMP-I/O                          | SMP-I/O                          |

| Base address  | 400 hex       | 420 hex               | 430 hex                          | 440 hex                          |

| Address range | 32 bytes      | 8 bytes               | 16 bytes                         | 16 bytes                         |

| Function      | E251 function | Expanded function     | Universal register,<br>channel 0 | Universal register,<br>channel 1 |

Sample values shown in **bold** type can be changed to meet the particular requirements.

1) Default setting: Disabled

The base addresses must be whole-number multiples of the address area (e.g., for channel 0: 400h, 420h, 440h and so on).

### Default settings in the "ASBIC channel settings" dialog field

| Parameter     | Default Setting |

|---------------|-----------------|

| ASBIC channel | Disabled        |

| Address mode  | SMP-I/O         |

| Base address  | 200 hex         |

### Default settings in the "general" dialog field

| Parameter                  | Default Setting     |

|----------------------------|---------------------|

| Parallel Output Port (POP) | 0011 0000 bin       |

| Memory address range       | Includes MMIO range |

### Settings on the parallel output port

| Bit | 7 | 6        | 5 | 4 | 3 | 2 | 1                                                                                                              | 0                                                                                                                                                      | Meaning:                                                                                                                                               |

|-----|---|----------|---|---|---|---|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |   |          |   |   |   |   |                                                                                                                |                                                                                                                                                        | Counting frequency, channel 0<br>(for frequency and pulse width measurement)                                                                           |

|     |   |          |   |   |   |   |                                                                                                                |                                                                                                                                                        | 2.5 or 4 MHz (depending on the operating mode)                                                                                                         |

|     |   |          |   |   |   |   |                                                                                                                |                                                                                                                                                        | 1: 1.25 or 2 MHz (depending on the operating mode)                                                                                                     |

|     |   |          |   |   |   |   |                                                                                                                |                                                                                                                                                        | Counting frequency, channel 1<br>(for frequency and pulse width measurement)                                                                           |

|     |   |          |   |   |   |   |                                                                                                                |                                                                                                                                                        | <ul><li>2.5 or 4 MHz (depending on the operating mode)</li><li>1.25 or 2 MHz (depending on the operating mode)</li></ul>                               |

|     |   |          |   |   |   |   |                                                                                                                |                                                                                                                                                        | Clock pulse supplied externally, channel 0<br>(With frequency and pulse width measurement,<br>the counting clock pulse can be supplied<br>externally.) |

|     |   |          |   |   |   |   |                                                                                                                |                                                                                                                                                        | 0: Internal<br>1: External                                                                                                                             |

|     |   |          |   |   |   |   |                                                                                                                | Clock pulse supplied externally, channel 1<br>(With frequency and pulse width measurement,<br>the counting clock pulse can be supplied<br>externally.) |                                                                                                                                                        |

|     |   |          |   |   |   |   |                                                                                                                | 0: Internal<br>1: External                                                                                                                             |                                                                                                                                                        |

|     |   |          |   |   |   |   | Ext. strobe, channel 0<br>Enable N track (zero marking pulse) input.<br>Otherwise ignore zero marking signals. |                                                                                                                                                        | Enable N track (zero marking pulse) input.                                                                                                             |

|     |   |          |   |   |   |   | <ul><li>0: Switch off N track</li><li>1: Switch on N track (default)</li></ul>                                 |                                                                                                                                                        |                                                                                                                                                        |

|     |   |          |   |   |   |   |                                                                                                                |                                                                                                                                                        | Ext. strobe, channel 1<br>Enable N track (zero marking pulse) input.<br>Otherwise ignore zero marking signals.                                         |

|     |   |          |   |   |   |   |                                                                                                                |                                                                                                                                                        | 0: Switch off N track<br>1: Switch on N track (default)                                                                                                |

|     |   |          | · |   |   |   |                                                                                                                |                                                                                                                                                        | Ext. clear, channel 0<br>Pulse on track N (zero marking pulse) resets the<br>counter.                                                                  |

|     |   |          |   |   |   |   |                                                                                                                |                                                                                                                                                        | 0: Function off<br>1: Function on                                                                                                                      |

|     |   | <u> </u> |   |   |   |   |                                                                                                                |                                                                                                                                                        | Ext. clear, channel 1<br>Pulse on track N (zero marking pulse) resets the<br>counter.                                                                  |

|     |   |          |   |   |   |   |                                                                                                                |                                                                                                                                                        | D: Function off<br>1: Function on                                                                                                                      |

For more details on how to handle these settings, see chapter 6.3.

## 5 Compatibility with SMP-E251

The SMP-E251-compatible registers and functions are located on the SMP-SFT251 in the address area of ASBIC channel 0. Since the address assignment is the same as that of the SMP-E251, software compatibility between the SMP16-SFT251 and the SMP-E251 is ensured. This compatibility is always ensured after a power-up or a hardware reset.

This address assignment can be changed with the BG\_Mode board-mode bit in control register 0 (bit 4). For the new address assignment, see chapter 6.1. This address assignment was selected to permit the registers of ASBIC channel 0 to be addressed with faster 16-bit accesses. However this means that, although the functions of the SMP-E251 are retained, the address assignment is no longer compatible with the SMP-E251.

When replacing an SMP-E251 with an SMP16-SFT251, remember that the SMP16 board no longer has jumpers. The addresses and various board modes are set with the SMP16-AKO auto-configuration software. See chapter 2.8.

In addition, the physical design of the shaft encoder inputs is not the same as that of the SMP-E251. Switch S1 or S2 can be used to choose between RS 422 and 24 V technology. In contrast to the SMP-E251, the 24 V inputs of the SMP16-SFT251 require more current due to the optical decoupling. See chapter 2.3.

## 6 **Programming the Board**

### 6.1 Register Overview

The SMP16 bus-ASIC ASBIC can be used to implement 4 channels with different base addresses (base addresses w to z). Remember that the base addresses must be multiples of the length of the corresponding address area.

#### Example:

Base address w includes 32 bytes (1Fh)  $\Rightarrow$  Addresses 400h, 420h, 440h, etc. can be used for base address w.

#### ASBIC channel 0

There are two different address assignments for the registers of ASBIC channel 0. The "BG\_Mode" board-mode bit in control register 0 (bit 4) can be used to run the board as compatible with the SMP-E251 or to use expanded functions (SMP-E251 or SMP16-SFT251 mode). The board is always in SMP-E251 mode (BG\_Mode = "0") after power-up or a hardware reset.

When SMP-E251 is selected, ASBIC channel 0 (base address w) can only be addressed with 8-bit accesses. The resulting address assignment of ASBIC channel 0 is shown below.

| Address          | I/O Unit               | Function                              |                                   |  |

|------------------|------------------------|---------------------------------------|-----------------------------------|--|

| Assignment (Hex) |                        | Write                                 | Read                              |  |

| Base Address w   | Counter 0              | SW strobe command 1)                  | Interrupt register (counter 0)    |  |

| w + 1            |                        | Counter byte 0 <sup>1)</sup>          | Zero-marking-pulse buffer, byte 0 |  |

| w + 2            |                        | Counter byte 1 <sup>1)</sup>          | Zero-marking-pulse buffer, byte 1 |  |

| w + 3            |                        | Counter byte 2 <sup>1)</sup>          | Zero-marking-pulse buffer, byte 2 |  |

| w + 4            |                        | Counter byte 3 <sup>1)</sup>          | Zero-marking-pulse buffer, byte 3 |  |

| w + 5            |                        | Mode register 1)                      | Reserved                          |  |

| w + 6            | Board control counters | Control register 0                    | Status register 0                 |  |

| w + 7            | 0 and 1                | Reset alarm bits                      | Status register 1                 |  |

| w + 8            | Counter 1              | SW strobe command 1)                  | Interrupt register (counter 1)    |  |

| w + 9            |                        | Counter byte 0 <sup>1)</sup>          | Zero-marking-pulse buffer, byte 0 |  |

| w + A            |                        | Counter byte 1 <sup>1)</sup>          | Zero-marking-pulse buffer, byte 1 |  |

| w + B            |                        | Counter byte 2 <sup>1)</sup>          | Zero-marking-pulse buffer, byte 2 |  |

| w + C            |                        | Counter byte 3 <sup>1)</sup>          | Zero-marking-pulse buffer, byte 3 |  |

| w + D            |                        | Mode register 1)                      | Reserved                          |  |

| w + E            | Counter 0              | SW clear command <sup>1) 2)</sup>     | Reset zero-marking-pulse latch    |  |

| w + F            | Counter 1              | SW clear command <sup>1) 2)</sup>     | Reset zero-marking-pulse latch    |  |

| w + 10           | Board control          | SW strobe command for both channels   | Reserved                          |  |

| w + 11           | Counter 0              | Enable one-time counter <sup>2)</sup> | Cancel counter write protection   |  |

| w + 12           | Counter 1              | Enable one-time counter <sup>2)</sup> | Cancel counter write protection   |  |

| w + 13           | Counters 0 and 1       | Reserved                              | Disable one-time counter          |  |

| w + 14           | Board control          | Enable zero-marking-pulse inputs      | Reserved                          |  |

| Address I/O Unit |           | Function             |          |  |

|------------------|-----------|----------------------|----------|--|

| Assignment (Hex) |           | Write                | Read     |  |

| w + 15           | Counter 0 | SW reload command 1) | Reserved |  |

| w + 16           | Counter 1 | SW reload command 1) | Reserved |  |

| w + 17 to 1F     |           | Reserved             | Reserved |  |

1) Not possible when write protection is set

2) The access triggers the function. Use the value "00H" for write accesses. Use any value for read accesses.

3) When hardware support is activated, an arriving zero-marking-pulse signal triggers write protection. See chapter 6.3.4.

When expanded mode (BG\_Mode = 1) is used, the registers in channel 0 can only be addressed with 16-bit accesses. The address assignment is shown below.

| Address          | I/O Unit          | Function                                |                                |

|------------------|-------------------|-----------------------------------------|--------------------------------|

| Assignment (Hex) |                   | Write                                   | Read                           |

| Base address w   | Counter 0         | Command register, low byte              | Interrupt register (counter 0) |

| w + 1            | Counter 1         | Command register, high byte             | Interrupt register (counter 1) |

| w + 2            | Counter 0         | Counter byte 0 <sup>1)</sup>            | Zero-markpulse buffer, byte 0  |

| w + 3            |                   | Counter byte 1 <sup>1)</sup>            | Zero-markpulse buffer, byte 1  |

| w + 4            | Counter 0         | Counter byte 2 <sup>1)</sup>            | Zero-markpulse buffer, byte 2  |

| w + 5            |                   | Counter byte 3 <sup>1)</sup>            | Zero-markpulse buffer, byte 3  |

| w + 6            | Counter 1         | Counter byte 0 <sup>1)</sup>            | Zero-markpulse buffer, byte 0  |

| w + 7            |                   | Counter byte 1 <sup>1)</sup>            | Zero-markpulse buffer, byte 1  |

| w + 8            | Counter 1         | Counter byte 2 <sup>1)</sup>            | Zero-markpulse buffer, byte 2  |

| w + 9            |                   | Counter byte 3 <sup>1)</sup>            | Zero-markpulse buffer, byte 3  |

| w + A            | Control counter 0 | Mode register <sup>1)</sup> , channel 0 | Status register 0              |

| w + B            | Control counter 1 | Mode register <sup>1)</sup> , channel 1 | Status register 1              |

| w + C            | Board control     | Control register 0                      | Reserved                       |

| w + D            |                   | "0000000b"                              |                                |

| w + E to 1F      |                   | Reserved                                | Reserved                       |

1) Not possible when write protection is set

#### Caution

Some of the reserved addresses of ASBIC channel 0 are used for testing and factory settings. Never write access these areas since this might render the board useless.

### **ASBIC channel 1**

| Address          | I/O Unit      | Unit Function                  |                                |  |

|------------------|---------------|--------------------------------|--------------------------------|--|

| Assignment (Hex) |               | Write                          | Read                           |  |

| Base address x   | Board control | Control register 1 (low byte)  | Control register 1 (low byte)  |  |

| x + 1            |               | Control register 1 (high byte) | Control register 1 (high byte) |  |

| x + 2            | Board control | Control register 2 (low byte)  | Control register 2 (low byte)  |  |

| x + 3            |               | Control register 2 (high byte) | Control register 2 (high byte) |  |

| x + 4            | Board control | Interrupt mask (low byte)      | Interrupt mask (low byte)      |  |

| x + 5            |               | Interrupt mask (high byte)     | Interrupt mask (high byte)     |  |

| x + 6            | Board control | Clear register (low byte)      | Status register 2 (low byte)   |  |

| x + 7            |               | Clear register (high byte)     | Status register 2 (high byte)  |  |

### ASBIC channel 2

| Address          | I/O Unit             | Function        |                 |  |

|------------------|----------------------|-----------------|-----------------|--|

| Assignment (Hex) |                      | Write           | Read            |  |

| Base address y   | Channel 0            |                 | UREG_00, byte 0 |  |

| y + 1            | Universal register 0 |                 | UREG_00, byte 1 |  |

| y + 2            |                      |                 | UREG_00, byte 2 |  |

| y + 3            |                      |                 | UREG_00, byte 3 |  |

| y + 4            | Channel 0            | UREG_10, byte 0 | UREG_10, byte 0 |  |

| y + 5            | Universal register 1 | UREG_10, byte 1 | UREG_10, byte 1 |  |

| y + 6            |                      | UREG_10, byte 2 | UREG_10, byte 2 |  |

| y + 7            |                      | UREG_10, byte 3 | UREG_10, byte 3 |  |

| y + 8            | Channel 0            |                 | UREG_20, byte 0 |  |

| y + 9            | Universal register 2 |                 | UREG_20, byte 1 |  |

| y + A            |                      |                 | UREG_20, byte 2 |  |

| y + B            |                      |                 | UREG_20, byte 3 |  |

| y + C to F       |                      | Reserved        | Reserved        |  |

### **ASBIC channel 3**

| Address          | I/O Unit             | Function        |                 |  |

|------------------|----------------------|-----------------|-----------------|--|

| Assignment (Hex) |                      | Write           | Read            |  |

| Base address z   | Channel 1            |                 | UREG_01, byte 0 |  |

| z + 1            | Universal register 0 |                 | UREG_01, byte 1 |  |

| z + 2            |                      |                 | UREG_01, byte 2 |  |

| z + 3            |                      |                 | UREG_01, byte 3 |  |

| z + 4            | Channel 1            | UREG_11, byte 0 | UREG_11 byte 0  |  |

| z + 5            | Universal register 1 | UREG_11, byte 1 | UREG_11, byte 1 |  |

| z + 6            |                      | UREG_11, byte 2 | UREG_11, byte 2 |  |

| z + 7            |                      | UREG_11, byte 3 | UREG_11, byte 3 |  |

| z + 8            | Channel 1            |                 | UREG_21, byte 0 |  |

| z + 9            | Universal register 2 |                 | UREG_21, byte 1 |  |

| z + A            | ]                    |                 | UREG_21, byte 2 |  |

| z + B            |                      |                 | UREG_21, byte 3 |  |

| z + C to F       |                      | Reserved        | Reserved        |  |

#### Note:

ASBIC channels 1 to 3 can be addressed with both 8-bit and 16-bit accesses. With 8-bit accesses, the low byte must first be written to/read from the lower address and then the high byte written to/read from the higher address.

## 6.2 Reset Reactions

The board can be reset with a hardware reset via the SMP16 bus.

### Status after reset/initialization

- All registers are cleared. Both counters are reset to "00000000hex."

- The front LEDs are off.

## 6.3 Function Description

### 6.3.1 Reading the Counter Status

The counter states cannot be read directly from the counter. Before the counter status can be read, it must be saved in a register. The "zero-marking-pulse-buffer" registers and the universal registers are used for this purpose. See chapter 6.1.

The counter status is transferred to the zero-marking-pulse buffer when a zero-marking pulse arrives or an SW-strobe occurs. Depending on the status of the BG\_Mode bit, the buffer can then be read with byte or word-accesses (see chapter 6.1). The read sequence is unimportant.

#### Note:

SW strobe will only work with operating mode "position acquisition with hardware support" when write protection of the particular channel is disabled (see chapter 6.3.4).

Chapters 6.3.8 and 6.3.9 explain how the universal registers function.

### 6.3.2 Loading the Counters

Both counters can be preloaded with start values. A counter-load register is assigned to each counter for this purpose. The data that will be loaded to the counter are intermediately stored in this register until the next loading procedure occurs. Actual loading of the counter differs depending on the status of the BG\_Mode board mode bit (see also chapter 6.4.2).

### BG\_Mode = "0"

In this case, the counter can only be addressed with 8-bit accesses as described in chapter 6.1. Each byte is loaded directly to the counter. The order in which the bytes are written to the counter is unimportant.

#### Note:

In this board mode, the counters should only be loaded when no counting signals are queued on the inputs. Otherwise, the counter states may no longer be consistent.

#### BG\_Mode = "1"

In this board mode, ASBIC channel 0 can only be addressed with 16-bit accesses (see chapter 6.1). The data must be written to the address of the counters in the following order: high word first (counter bits 16 to 31) and low word second (counter bits 0 to 15). The high word is first stored intermediately in the counter-load register. Not until the low word is loaded to the counter is the counter synchronously loaded with all 32 bits. This type of counter loading ensures that all four counter bytes arrive at the counter at the same time and that all four bytes are available simultaneously for the counting procedure. This makes it possible to load the counter synchronously even during running operation.

#### Note:

Loading the counters will only work with operating mode "position acquisition with hardware support" when write protection of the particular channel is disabled (see chap. 6.3.4).

#### 6.3.3 Position Acquisition via Shaft Encoder Edge Evaluation

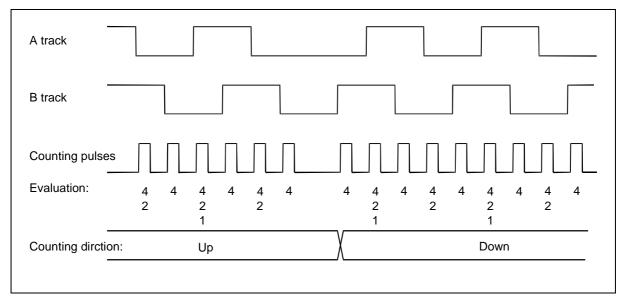

A two-track incremental shaft encoder with zero-marking track can be connected to each channel (see also chapter 2.5.1). The counting impulses and counting direction are determined from the signals of the A and B tracks. This is done by evaluating the edges of the individual tracks. The following figure illustrates this principle.

Figure 6.1 Shaft encoder edge evaluation

The counting direction is determined by the relationship of the A track to the B track. The number of counting pulses depends on which type of edge evaluation was set in the mode registers of the counters (see chapter 6.4.1).

- Quadruple edge evaluation counts each edge on the A and the B tracks.

- Double edge evaluation only counts the change in edge on the A track.

- Single edge evaluation only counts the rising edge of the A track.

#### Note:

With single edge evaluation, the counter may drift off slowly in one counting direction (due to operating mode) even the shaft encoder axis is at a standstill. This occurs when vibrations from the plant cause the shaft encoder to always have an edge change on the A track.

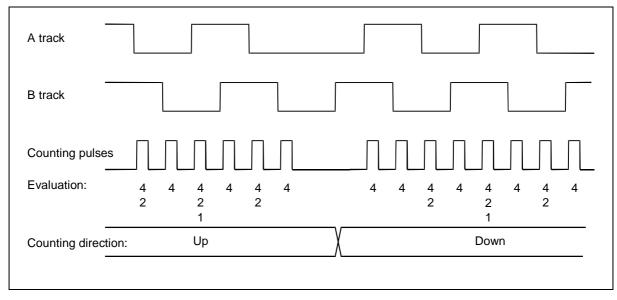

The hysteresis function which can be activated in the mode registers of the counters (see also chap. 6.3.11) can be used to counteract this behavior and suppress the first counting pulse after a reverse in the direction of rotation. The following figure illustrates use of the hysteresis function.

Figure 6.2 Shaft encoder edge evaluation with the hysteresis function

### 6.3.4 Position Acquisition with Hardware Support

In this mode, the board offers the user support in processing the registers. The zero-marking-pulse input of the respective channel plays an important role. An arriving zero marking pulse triggers the following events on the board.

- The current counter status is stored in the zero-marking-pulse buffer where it can then be read.

- Counter write protection is set so that the zero-marking-pulse buffer cannot be overwritten by an event. (It cannot be overwritten by a zero-marking-pulse signal or SW strobe.) The counter itself is also protected from write accesses or "clear" events (see chapter 6.3.10). Write protection can be reset with the "cancel counter write protection" command (see chapter 6.3.7).

- The following status bits are set for each of the two counting channels.

| Status Bits, Counting Channel 0              | Status Bits, Counting Channel 1              |